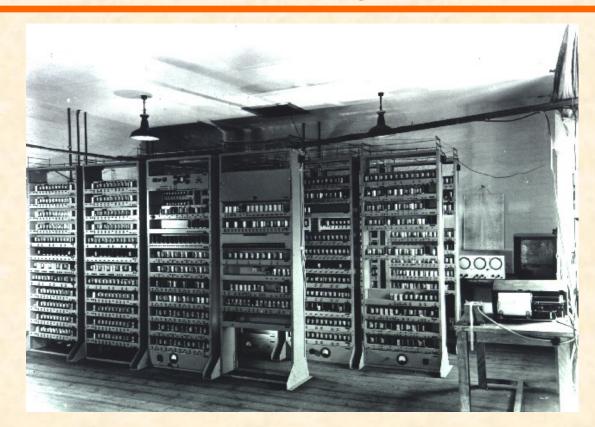

### **Electronic Delay Storage Automatic Calculator**

# Reconstructing EDSAC Andrew Herbert 25<sup>th</sup> April 2024

### **The Project**

Build a working reconstruction of Cambridge University's EDSAC Computer as it was when it provided the world's first computing service in 1950/51.

### Why Build a Replica of EDSAC?

- To celebrate an early triumph of British computer technology - and the creation of the world's first practical electronic stored program computer.

- To give us a better understanding of our computer heritage and create a new archive of historic material about early computing.

- To revive disappearing expertise and learn about the technical challenges faced by the early computer pioneers.

- A valuable new and living educational resource at The UK National Museum of Computing.

### **EDSAC** Achievements

- 1. The first *practical* general purpose, stored program, electronic, digital computer.

- provided a computing service for the University of Cambridge.

- 2. The invention of software:

- first machine to read in symbolic programs.

- Extensive library of "subroutines".

- 3. Transformed science:

- 1500 times faster than the mechanical calculators it replaced.

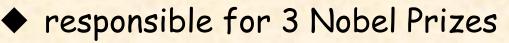

### **EDSAC Nobel Prize Winners**

Martin Ryle & Anthony Hewish

Radio Astronomy

Photo: John T Scott, Physics Today Collection

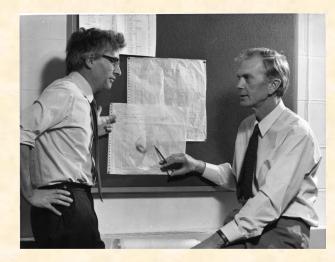

Sir John Carew Eccles

Andrew Fielding Huxle

#### John Eccles, Alan Hodgkin, Andrew Huxley

Signalling in the Nervous System

Photo: Nobel Foundation

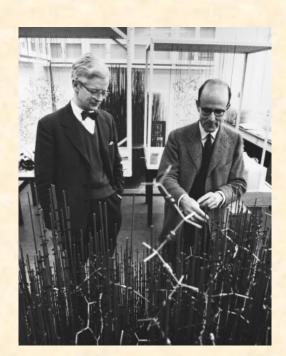

John Kendrew and Max Perutz Structure of Globular Proteins Photo: Medical Research Council

### **Lyons and Computing**

- Lyons interested in automatic information processing low margins business + rising staff costs

- Von Neumann "First Draft of a Report on EDVAC" was circulating in UK in 1946/7 - people were thinking about "computers" and how they might be used

- Lyons executives visited USA to learn about computers

- Told to visit M.V. Wilkes at Cambridge University Mathematical Laboratory as EDSAC ahead of USA efforts

### **EDSAC & LEO**

- Prototype for LEO

- Improved engineering for greater reliability

- Added features for business computing

- I/O

- Decimal computation

- Pinkerton visited M.V. Wilkes at Cambridge Mathematical Laboratory to see EDSAC

- Ernest Lenaerts assigned to EDSAC Project

- Funds donated to Mathematical Laboratory to help project progress more rapidly

### **The EDSAC Story**

First Draft of a Report on the EDVAC

by

John von Neumann

Contract No. W-670-ORD-4926

Between the

United States Army Ordnance Department

and the

University of Pennsylvania

### M.V. Wilkes (1913-2010)

- B.A. Mathematics, St John's College, Cambridge

- PhD, Physics, Cavendish Laboratory

- War time radar expert

- Director of Cambridge Mathematical Laboratory

- John Von Neumann: "Draft Report on the EDVAC"

- Princeton Conference 1948

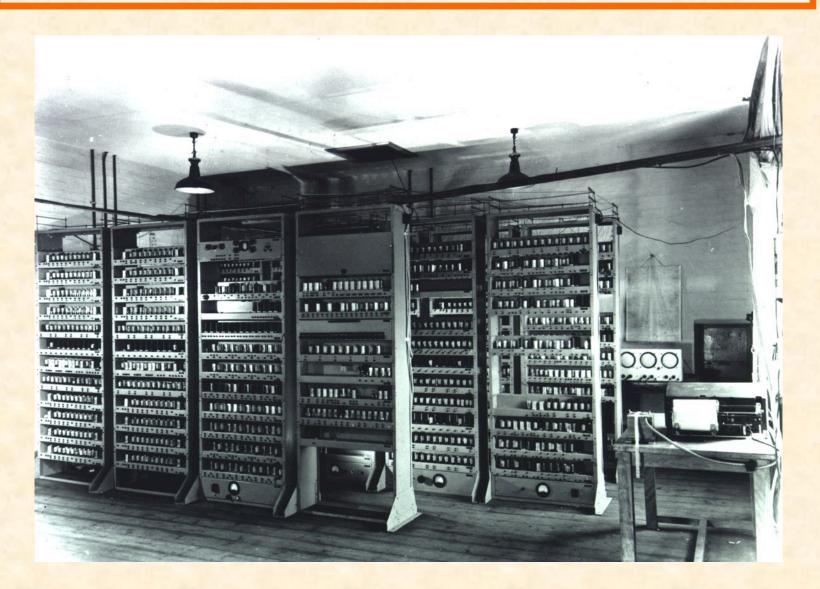

### **EDSAC (1949)**

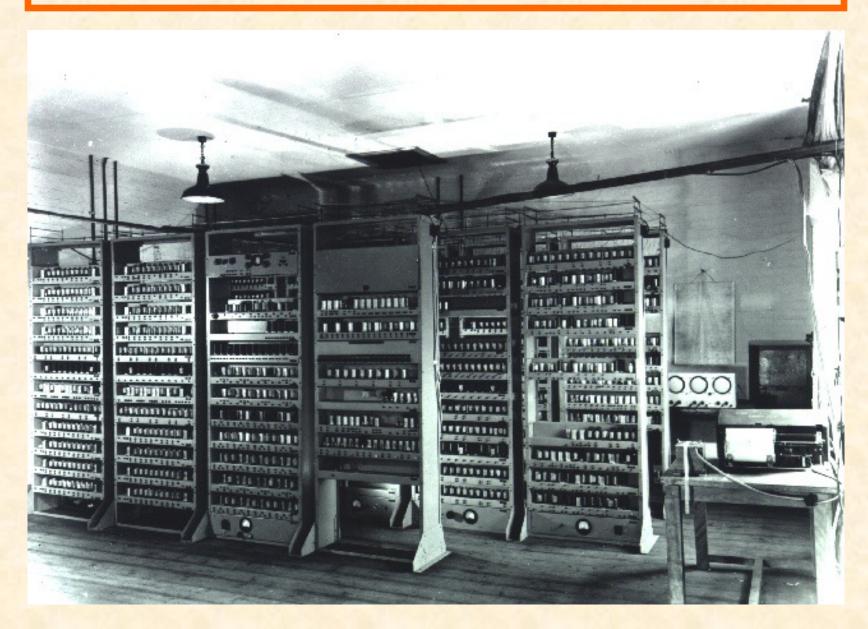

### **EDSAC**

Automatic Digital Computers, M.V. Wilkes, 1956

Dodd & Glennie ARE Report 7/51 1951

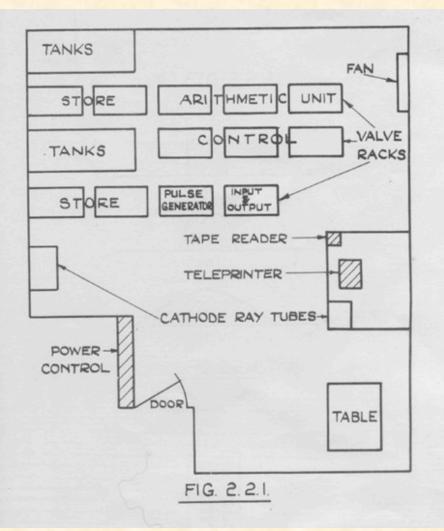

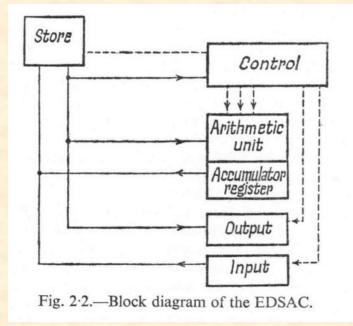

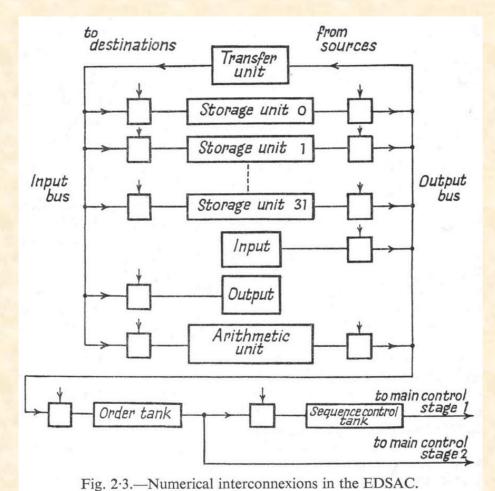

### **EDSAC** Architecture

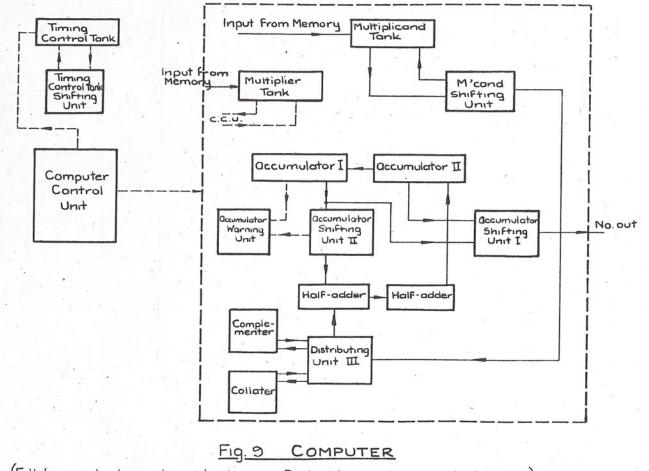

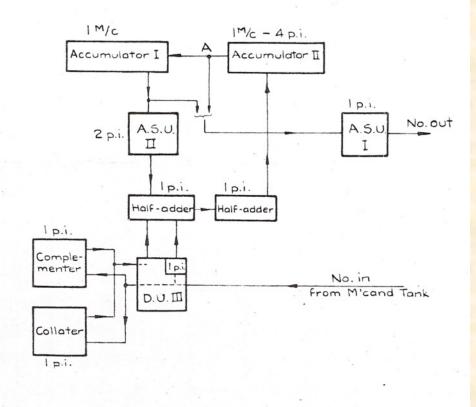

Automatic Digital Computers, M.V. Wilkes, 1956

### **Computer Memory in 1949**

- Too expensive to build an electronic memory.

- 5 tubes per bit \* 17 \* 1024

= 79,000 tubes.

- Acoustic delay lines.

- Williams (cathode ray) tubes.

- Rotating magnetic drums.

- All were complex, expensive and unreliable.

- All limited speed of the "computer".

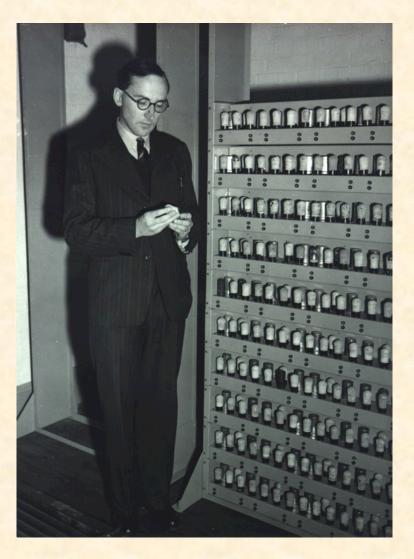

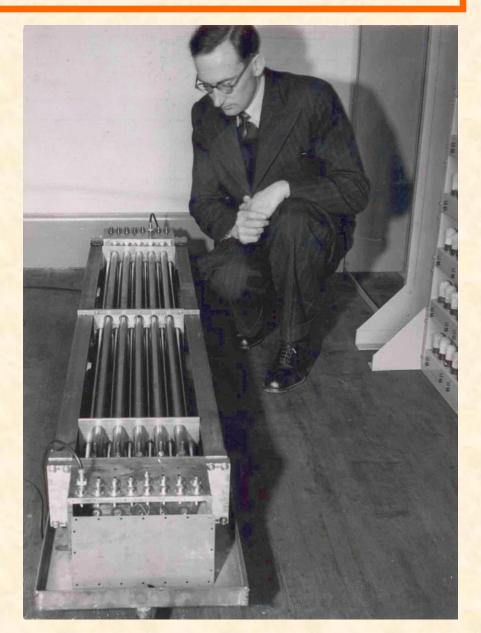

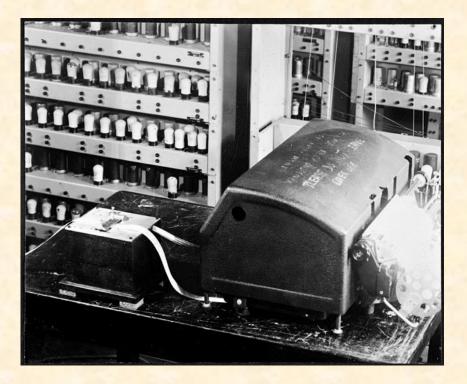

### **EDSAC Acoustic Delay Lines**

Maurice Wilkes with a battery of 16 storage tanks, each holding 16 x 36 bit words.

The 5 ft steel tubes contain mercury as the acoustic delay medium.

Designed by T. Gold.

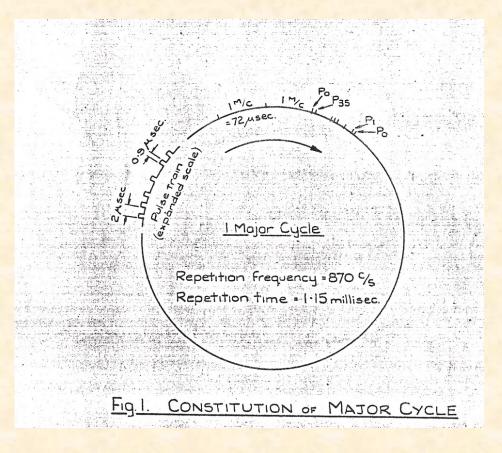

### **Serial Computing**

#### Most of EDSAC is serial Process one bit of a word at the time Reduces number of components needed

|                      | L1M/c1                          | 1                    |

|----------------------|---------------------------------|----------------------|

| Clock and the second | R P2 P3 P4 P20P21 P35B1R P2     | in the second second |

| Clock pulses .       | erc.                            | 1.1.1                |

| Digit pulse Do -     |                                 |                      |

|                      |                                 |                      |

| Digit pulse Dzo-     |                                 |                      |

| FIQ. 2. SYSTE        |                                 |                      |

| FIG. L. SYSTE        | MS OF REGULAR REPETITIVE PULSES |                      |

From Edsac Report

### **Decoding and Coincidence**

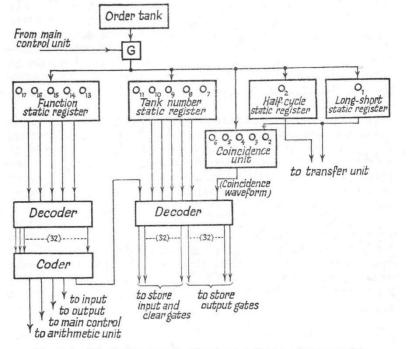

Fig. 2.4.—Block diagram showing how orders are interpreted in Stage II of the control sequence.

Have to go parallel to decode function number and memory address

Automatic Digital Computers, M.V. Wilkes, 1956

### **Building the Replica**

### Authenticity

We don't have a complete blueprint, so we aim to...

- be consistent with photographs and contemporary records.

- use period components and circuits when available and suitable.

- Use functionally equivalent modern components otherwise.

- adhere to EDSAC "principles" when filling in gaps.

### **Documents & Knowledge Acquisition**

- Original (incomplete) technical description

& logical design outline from Cambridge

Computer Laboratory archives.

- Original photographs & published papers.

- Recollections of pioneers.

- Found cache of ~20 circuit diagrams for "the later EDSAC".

- EDSAC ran for 10 years so need to understand the evolution of the machine (our target: 1950/51).

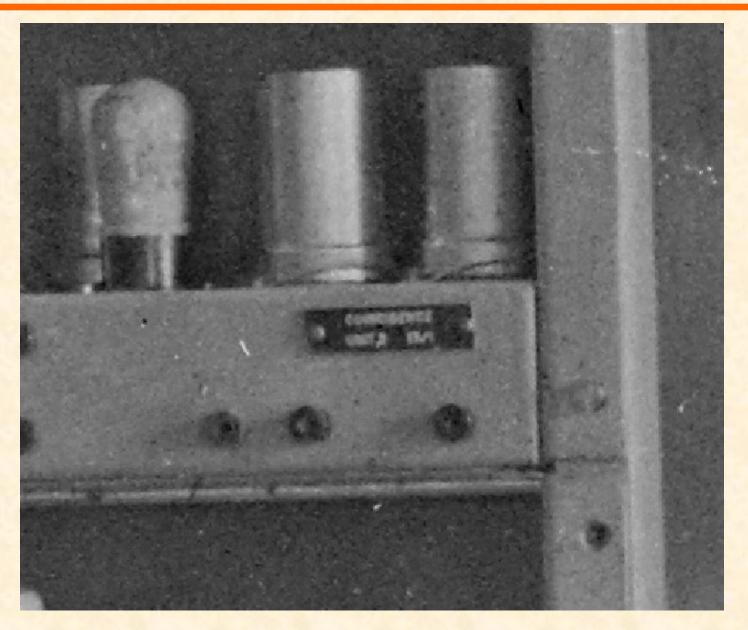

### **Mechanical Design**

- Scanning and measuring from photos.

- 12 racks, 142 chassis ("panels").

- An original chassis exists to measure.

- Drawn up using CAD.

- At the outset we didn't know how many different types of chassis there were, or where they were placed in the racks.

### **Rack and Chassis Manufacturing**

#### Teversham Engineering, Cambridge

### **Logic Design & Simulation**

- Need to know how EDSAC works in detail

- Incomplete & inconsistent diagrams

- Evidence of much re-design during commissioning

- Need to extrapolate undocumented areas of logic

- Simulation essential to give confidence before committing to building anything

### **Typical Logical Diagram**

(Full lines indicate number pulse trains. Broken lines indicate control signals)

#### From EDSAC Report

### **Typical Timing Diagram**

FIG. 13. DELAYS IN COMPUTER

#### From EDSAC Report

### **Logic Simulation**

- Bill Purvis wrote a simulator for whole logic can run a program, very slowly.

- Now translated to Verilog and running on an FPGA.

| 155          | MC 156     | MC             | 157 | MC | 158 | MC          | 159 | 9MC      |

|--------------|------------|----------------|-----|----|-----|-------------|-----|----------|

| Start        |            |                |     |    |     |             |     | <u> </u> |

| S1<br>S2     |            |                |     |    |     |             |     |          |

|              |            |                | Π   |    |     |             |     |          |

| Rpulse<br>EP |            |                |     |    |     |             |     | -        |

| G12          |            |                |     |    |     |             |     | -        |

| G13          |            |                |     |    |     |             |     |          |

| CG+<br>MOB   |            | L              |     |    |     |             |     | +        |

| Order        |            |                |     |    |     |             |     |          |

| Counter      |            |                |     |    |     |             |     |          |

| MIB          |            |                | 000 |    |     |             |     |          |

|              |            | - <b> </b> UUL |     |    |     | <b>↓</b> ]└ |     |          |

| Acc1<br>Acc2 | JL_JULIJUL |                |     |    |     |             |     | ┿╝└╡     |

| Mcand        |            |                |     |    |     |             |     |          |

| Adder-A      |            |                |     |    |     |             |     |          |

| Adder-B      | 0.000.00   |                |     |    |     |             |     |          |

| Adder-Sum    |            |                |     |    |     |             |     |          |

|              |            |                |     |    |     |             |     |          |

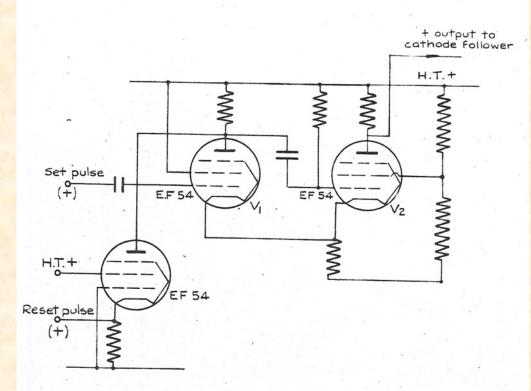

### **Electronic design**

- EDSAC was built by radio and radar engineers with no knowledge of "digital logic" as we understand it today.

- "Computing with waveforms", F.C. Williams

- Common circuit elements aid identification: flip-flop, inverter, short delay, pulse amplifier.

- Lots of circuit simplification to reduce valve count and stage delays but introduces problems with noise.

- System requires careful tuning to ensure signals arrive "on time".

### **Typical Circuit Diagram**

From EDSAC Report

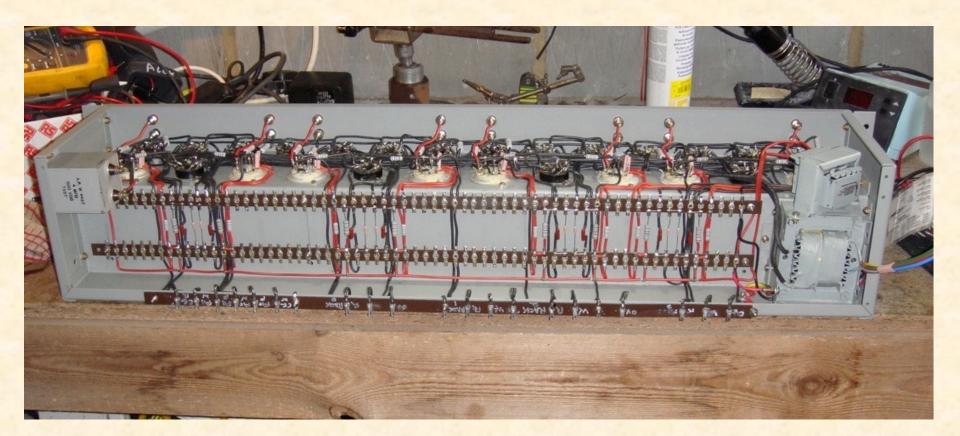

### **Mapping Logic to Chassis**

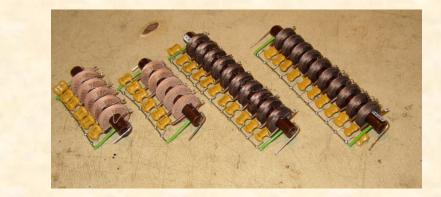

### **Acquisition of Parts**

- Many, but not all, thermionic valves are available commercially as "new old stock".

- B9G valve holders are problematic.

- Authentic 'period' resistors and capacitors are too unreliable to use.

- Hand made tag strips and coils.

### **Replica Chassis**

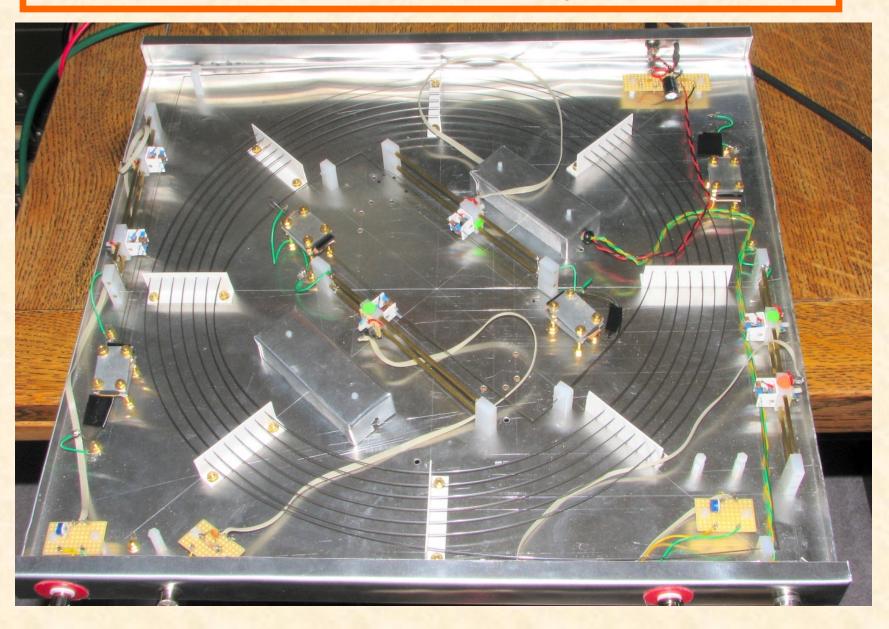

### **Replica Memory Tanks**

- Risky and costly to use mercury, except perhaps in one example tank.

- Temperature stability is a major issue.

- Precision engineering required: tubes and end plates - aligned to within 0.001" endto-end.

- Using magnetostrictive nickel delay lines as a reasonable alternative.

- Use semiconductor shift registers to get off the ground quickly.

### **Short Nickel Delay Line**

## **Programming EDSAC**

| UNIV                                      | ERSITY MATHEMATICAL L                                                                           |                          |                                                | The second                              |                             | #1 |

|-------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------|-----------------------------------------|-----------------------------|----|

| Calculation of                            | curves for y=12 etc.                                                                            |                          |                                                |                                         | - FEBT: 5= 512 5=11/2 Lunts |    |

| Calculates                                | A2, 125 vg, ) 64 vg<br>apre WSG :                                                               |                          |                                                | 15 Store                                | TITLE WRITTEN<br>ON TAPE    |    |

| -                                         | T N36.                                                                                          |                          |                                                | PF                                      |                             |    |

|                                           |                                                                                                 |                          |                                                | T 134 K                                 |                             |    |

|                                           |                                                                                                 |                          |                                                | P1024 F                                 |                             |    |

| Order                                     | Notes                                                                                           | Order                    | Notes                                          | T242K                                   | T144D                       |    |

| 0 P F<br>1 T 134 K                        | This                                                                                            | E V 2047 D<br>K 4095 D   | States at sin 2D == 2 (2 = 10 <sup>-10</sup> ) | C14D                                    |                             |    |

| 2 P x F                                   | x= 4f x 2048 this<br>F in 126                                                                   | S2 P & (FD)              | h = sin D × 32768<br>A starting value.         | C1430                                   | EISID                       |    |

| 3 T 126 K<br>4 P Y F                      | y = 2048 F.                                                                                     | 4 T 136 K                | )                                              | E HAR                                   |                             |    |

| 5 T 294 K                                 |                                                                                                 | 5 P F                    | S clears 2                                     | CHICAGO CONTRACTOR                      | E 144 K                     |    |

| 6 E 231 F<br>T 231 K                      |                                                                                                 | 6 P F<br>T 358 K         | · · · · ~                                      | TI26K                                   |                             |    |

| 8 A 231 F                                 |                                                                                                 | 8 A 243 F                | A second                                       | P., F                                   | rr                          |    |

| 9 G 165 F<br>0 A D                        |                                                                                                 | 9 T 126 K<br>0 T 323 K   |                                                |                                         |                             |    |

| 1 T 288 D                                 |                                                                                                 | 1/T 171 K                |                                                | PF                                      |                             |    |

| 2 A 235 F<br>3 G 91 F                     |                                                                                                 | 2 E 179 F                |                                                | T 370K                                  |                             |    |

| 4 A 288 D                                 |                                                                                                 | 4 T 179 K                |                                                |                                         |                             |    |

| 5 T D<br>6 0 241 F                        |                                                                                                 | 5 A 126 D<br>6 T 132 K   |                                                | P., F                                   |                             |    |

| 7 E 296 F                                 | - dut )                                                                                         | 7 P 10813 F              |                                                | TITIK                                   |                             |    |

| <sup>8</sup> $\phi$ F<br><sup>9</sup> W F | - Clarge do P & F shore<br>(clarge do P & F shore<br>to birth 0 + 32165<br>ΔFx 2048 = g (x - F) | 8 P 32000 F<br>9 T 317 K |                                                | T146D                                   | 22222                       |    |

| · P Sta F                                 | $\Delta F \times 2048 = g(x + \frac{F}{2}).$                                                    | 0 P 256 F                | 0 241 F                                        | E 378F                                  |                             |    |

| 1 T 329 K<br>2 A 126 D                    |                                                                                                 | 1 T 314 K<br>2 T 36 D    | T D<br>E 3/6 F                                 | T278K                                   |                             |    |

| 3 A 243 F                                 | A. 1. 11                                                                                        | 3 E 248 F                | T 366 K                                        | 101 101 101 101 101 101 101 101 101 101 |                             |    |

| 4 T 126 D<br>5 T 355 K                    | Sa'= no of steps before<br>goest value of int D                                                 | 4 T 248 K<br>5 H 36 D    | PNF                                            | H384 F                                  |                             |    |

| 6 A 128 D                                 |                                                                                                 | 6 V 288 D                | T 211 K) ton<br>S DSX<br>only                  | N 146D                                  |                             |    |

| 7 A 242 F<br>8 T 128 D                    |                                                                                                 | 7 T D<br>8 A 251 F       | E 144 K                                        |                                         |                             |    |

| T 128 K.                                  |                                                                                                 | 9 G 9/F                  | P F.                                           |                                         |                             |    |

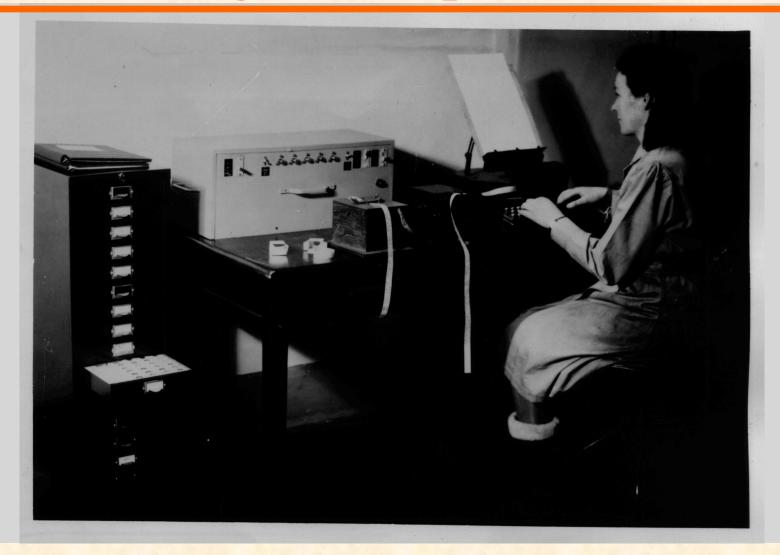

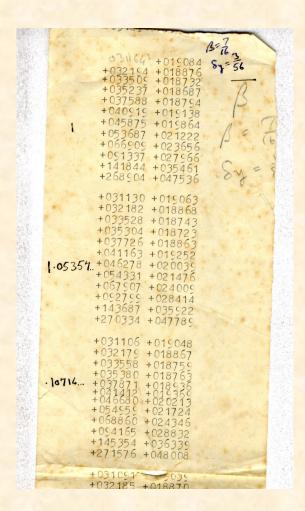

### **Program Preparation**

### **Operating EDSAC**

### Output

### **Initial Orders**

- Loaded on "START"

- Reads in user program

- Combined "assembler" and "linker"

- Extensive library of subroutines input, output, mathematical functions

- Alphanumeric source code

- Parametric addressing to allow position independent code

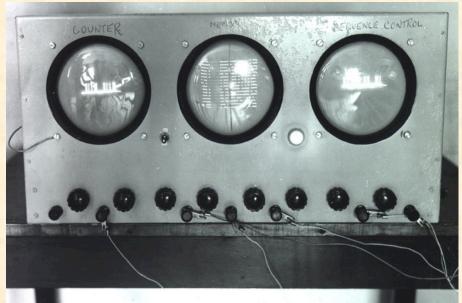

### Status (March 2024)

- 140 chassis built and tested of 142 total.

- Clock and Digit Pulse system working.

- Memory recirculation, addressing and coincidence working.

- Main control working.

- Transfer unit working.

- Delay line register stores working.

- Main store delay lines in commissioning.

- Systematic testing of arithmetic functions underway

- I/O and Initial Orders under construction

### **To Find Out More**

- Visit www.edsac.org web site

- Download EDSAC simulator from http://www.dcs.warwick.ac.uk/~edsac/